# Fixing BRexx on VM/370 (Or REXX and Bytecode) (Or CREXX - A REXX Architecture)

The 31st Annual Rexx Symposium

Adrian Sutherland • 29.09.2020 (Final) **WARNING:** We are going to cover this but in a <u>non-linear narrative structure</u> (!)

# Fixing BRexx on VM/370

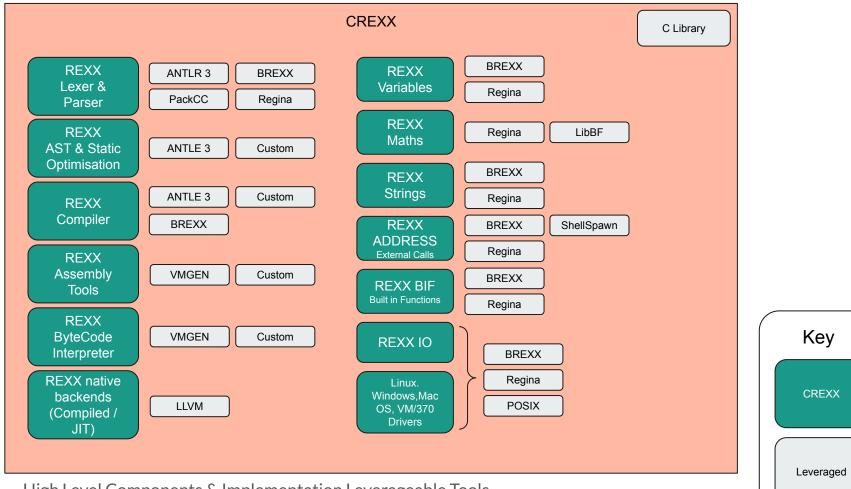

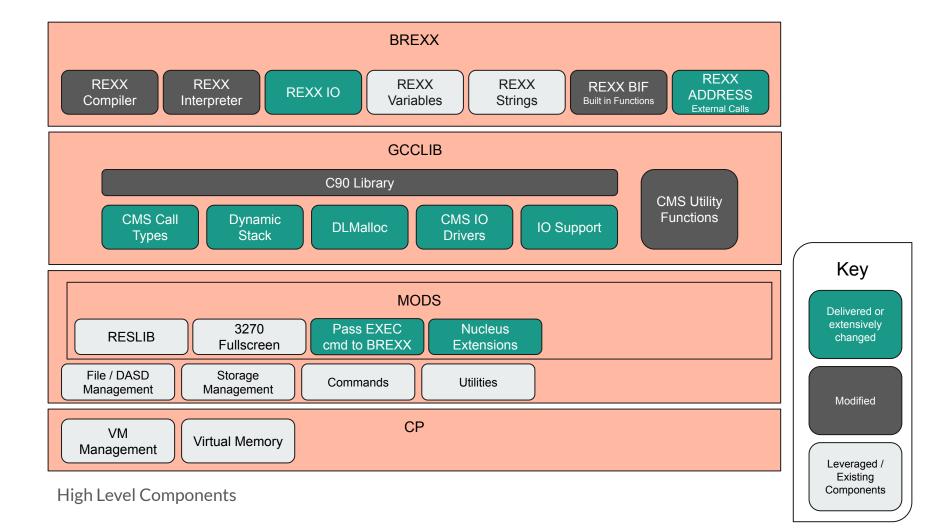

VM/370 DevOps GCCLIB - The C library **BREXX** - Internals and changes The CREXX Project - A REXX Architecture REXX - how can it be improved while keeping its essence, "to make programming

easier than before"? Next Up - The VM/370 interface to Rexx with Bob Bolch

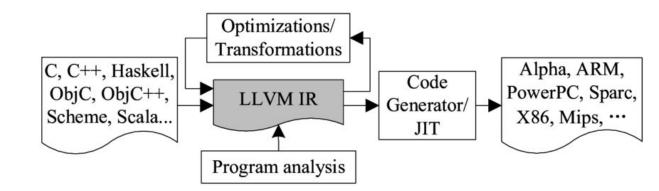

#### LLVM

The LLVM Project is a collection of modular and reusable compiler and toolchain technologies

https://llvm.org/

The core of LLVM is the intermediate representation (IR), a low-level programming language similar to assembly. IR is a strongly typed reduced instruction set computing (RISC) instruction set which abstracts away most details of the target. For example, the calling convention is abstracted through call and ret instructions with explicit arguments. Also, instead of a fixed set of registers, IR uses an infinite set of temporaries of the form %0, %1, etc.

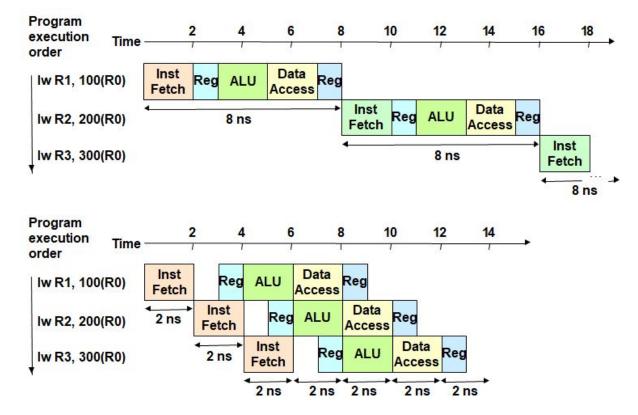

#### Pipelining

Conceptually a CPU executes instructions one after the other, however to get a performance boost instructions overlap in a "production line" (pipeline).

Pipeline lengths are currently typically 15 odd stages (Intel/ARM)

There are hazards that cause a pipeline stall (e.g. accessing information not yet written and conditional branching)

This is one reason why it is very hard to write modern assembler and efficient backends for different architectures (hence the use of LLVM). Another is CPU memory caching

However a journeyman programmer can do somethings!

#### Diagram from a Aharon Kupershtok lecture

#### Typical Bytecode Optimisation

- 1. Threaded code

- 2. Super-instructions / inlining

- 3. Top-of-stack in a register

- 4. Scheduling the dispatch of the next VM instruction

### In all about 2x faster than classic bytecode

We should be aiming for performance of only 2-5 times slower than native code

NOTE - We could be talking about any language ...

```

char code[] = {

ICONST_1, ICONST_2,

IADD, ...

}

char *pc = code;

```

```

/* dispatch loop */

while(true) {

switch(*pc++) {

case ICONST_1: *++sp = 1; break;

case ICONST_2: *++sp = 2; break;

case IADD:

sp[-1] += *sp; --sp; break;

...

}}

```

#### **Pure Bytecode**

```

void *code[] = {

&&ICONST_1, &&ICONST_2,

&&IADD, ...

}

void **pc = code;

/* implementations */

goto **(pc);

ICONST_1: pc++; *++sp = 1; goto **(pc);

ICONST_2: pc++; *++sp = 2; goto **(pc);

IADD:

pc++; sp[-1] += *sp; --sp; goto **(pc);

...

```

**Threaded Interpreter**

/\* SIMPLE \*/ A = 10 B = 5 SAY A + B

#### **REXX Assembler**

This is where optimisations become REXX specific ...

BREXX

Stack Based

• Leaves work to the interpreter

CREXX

- Register Based

- Trying to handle REXXisms at the low level

We need to get this right for LLVM ...

| NEWCLAUSE |     | .def ma | in: locals=3 {r1="A", r2="B"} |  |

|-----------|-----|---------|-------------------------------|--|

| CREATE    | "A" | ILOAD   | r1,10                         |  |

| PUSH      | 10  |         |                               |  |

| COPY      |     |         |                               |  |

| NEWCLAUSE |     | ILOAD   | r2,5                          |  |

| CREATE    | "B" |         |                               |  |

| PUSH      | 5   |         |                               |  |

| COPY      |     |         |                               |  |

| NEWCLAUSE |     | IADD    | r3,r1,r2                      |  |

| PUSHTMP   |     |         |                               |  |

| LOAD      | "A" |         |                               |  |

| LOAD      | "В" |         |                               |  |

| ADD       |     |         |                               |  |

| SAY       |     |         |                               |  |

| NEWCLAUSE |     | ISAY    | r3                            |  |

| IEXIT     |     | HALT    |                               |  |

|           |     |         |                               |  |

| BREXX     |     | CREXX   |                               |  |

|           |     |         |                               |  |

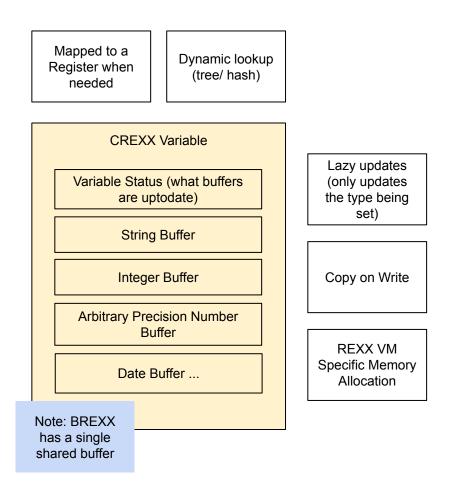

#### REXX Variable Types

- 1. Rexx is typeless ... and more than that conceptually all variables are strings

- 2. Rexx stems provide a flexible and arbitrary index scheme

- 3. VALUE(), INTERPRET(), and REXXSAA/EXECOMM all require dynamic variable name resolution

- 4. Performance requires compile time resolution of variable names and types, wherever possible

/\* SIMPLE2 \*/ ARG INDEX VAL DATA.INDEX = VAL SAY DATA.INDEX

> SIMPLE2 10 TEST

#### **REXX Assembler**

This is where optimisations become REXX specific ...

#### BREXX

- Stack Based

- Leaves work to the interpreter

CREXX

- Register Based

- Trying to handle REXXisms at the low level

We need to get this right for LLVM ...

| SCLOADr4,"DATA."* DATA. in const poolSCONCATr4,r4,r1* r4 is now "DATA.10"SRMAP1r3,r4* r3 is var DATA.10SLOADr3,r2*= VAL |

|-------------------------------------------------------------------------------------------------------------------------|

| SSAY r3<br>HALT                                                                                                         |

|                                                                                                                         |

| —                                      | REXX Assembler Variable Mapping                                             | /                                                                           |                                                                                     |  |

|----------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------|--|

|                                        | With Constant Pool                                                          | VAL                                                                         |                                                                                     |  |

|                                        | * Map RegisterN to DATA<br>SCRMAP rN,"DATA"                                 | X                                                                           |                                                                                     |  |

| REXX                                   | * Map RegisterN to DATA."registerA"<br>SCRMAP1 rN,"DATA",rA                 | TEST                                                                        |                                                                                     |  |

|                                        | * Map RegisterN to DATA."registerA"."registerB"<br>SCRMAP2 rN,"DATA",rA, rB | .def main: locals=4 {r1="INDEX", r2="VAL"}<br>ARGUPPER r4<br>TR_SPACE r1,r4 |                                                                                     |  |

| This is wher<br>REXX specit            | etc.                                                                        | TR_END r2,r                                                                 |                                                                                     |  |

|                                        | Without Constant Pool                                                       |                                                                             |                                                                                     |  |

| BREXX                                  | * Map RegisterN to "registerA"<br>SRMAP1 rN,rA                              |                                                                             |                                                                                     |  |

| <ul><li>Stack</li><li>Leav</li></ul>   | * Map RegisterN to "registerA"."registerB"<br>SRMAP2 rN,rA,rB               | C                                                                           |                                                                                     |  |

| CREXX                                  | etc.                                                                        | SCONCAT r4,r<br>SRMAP1 r3,r                                                 | DATA." * DATA. in const pool<br>4,r1 * r4 is now "DATA.10"<br>4 * r3 is var DATA.10 |  |

|                                        | REXX Assembler Variable Type Control                                        | SLOAD r3,r                                                                  | 2 * = VAL                                                                           |  |

| <ul><li>Regise</li><li>Tryir</li></ul> | IREADY rN<br>FREADY rN * TBD - how to control precision<br>SREADY rN        | SSAY r3<br>HALT                                                             |                                                                                     |  |

| the le                                 | DREADY rN * Date why not?!                                                  | CREXX                                                                       |                                                                                     |  |

| We need to                             | ADD rN,RM * Readies both registers as integers (unlike IADD)                |                                                                             |                                                                                     |  |

High Level Components & Implementation Leverageable Tools

## **Other REXX Considerations**

- 1. Global Variables vs. EXPOSEd Variables

- 2. PARSE vs Regular Expressions

- 3. Shared variables across modules

- 4. Mixed-case lexing (and other funnies)

- 5. OOREXX How to make it "easier". E.g.

- a. Static or Dynamic

- b. Class Hierarchies or Interfaces?

- 6. What should "easier" IO look like? For example are pipes a more "REXX" IO metaphor?

Is this accusation fair: just bolting on functions is rather "C" ...

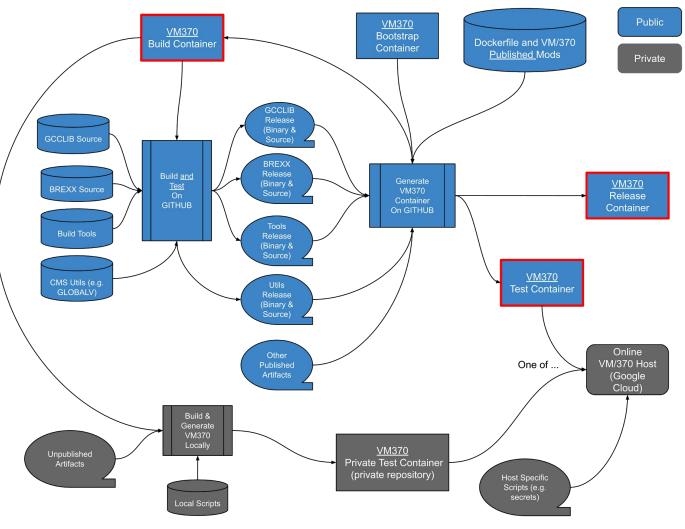

DevOps - "a set of practices intended to reduce the time between committing a change to a system and the change being placed into normal production, while ensuring high quality"

Len Bass, Ingo Weber, and Liming Zhu

#### Technology

- Hercules S/370 Emulator

- VM/370 "Six Pack"

- Docker Containers

- Docker Hub

- GitHub Repository

- GitHub Actions

- Google Cloud Repository

- Google Cloud Container Optimised OS for hosting VM/370 Host

- YATA & Herccontrol

- REXX & C Test Suites

## **Adrian Sutherland**

- CTO of Jumar Technology, specialists in legacy modernisation

- Journeyman Architect

- Keeps "hands-on" through numerous projects, from Raspberry PI toys and Domain Specific Languages to open architectural papers and other assets.

adrian@sutherlandonline.org

adrian.sutherland@jumar-technology.com

### Thanks to ...

- Bob Bolch for all the hard work on VM/370, help with my very poor S/370 Assembler, and always debating to make things better! Without his help this would not have been possible

- René Jansen for all his encouragement, and bringing together the REXX test Suite

And everyone else - whose ideas I have misused!

## Questions

adrian@sutherlandonline.org adrian.sutherland@jumar-technology.com